Buck converter specification

변환기 예제는 아래와 같은 사양으로 디자인되어 있습니다.

• Input supply voltage: 5 V

• Output voltage: 3.3 V

• Maximum current: 0.5 A

• Target ripple: 0.5% (16.5 mV)

• Overshoot (50% load step): 5 mV

• Control mode: Voltage, digital

• Switching frequency: 200 kHz

• Sampling frequency: 200 kHz

• Crossover frequency: 8 kHz

• Phase margin at crossover: 50 degrees

• Duty cycle limit: 90%

디스커버리 키트의 스위치에는 다음과 같은 특성이 있습니다.:

• Primary switch resistance: 56 mΩ

• Primary rise time: 20 ns

• Primary fall time: 20 ns

• Parasitic capacitance: 79 pF

• Secondary voltage drop: 0.02 V Output filter characteristics:

• Ripple: 0.125 A pk-pk

• L inductance: 51 µH

• L DCR: 380 mW

• C capacitance: 100 µF

• C ESR: 170 mW

ADC 및 PWM 특성은 다음과 같습니다.:

• PWM master clock frequency: 5440 MHz (HR Timer at 170 MHz, x32 resolution)

• PWM period count: 27200 (for 200 kHz frequency)

• ADC resolution: 12 bits

• ADC full scale voltage: 3.3 V

• ADC input voltage divider ratio R2/(R1+R2): 0.19

ADC 풀 스케일 디지털 코드는 212-1 = 4095입니다. 따라서 3.3V의 목표 출력 전압에 해당하는 기준 값(REF)은 0.19 x 4095 = 778입니다.

Controller design

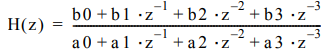

전압 컨트롤러는 유형 III 아날로그 보상기를 기반으로 합니다. 디지털 영역에서 이것은 3개의 극과 3개의 0이 있는 3차 IIR 필터를 사용하여 근사하므로 3p3z 보정기라는 이름이 붙습니다.

세 개의 극과 두 개의 영점 배치는 아날로그 영역에서 수행됩니다. 그 다음 전달 함수는 여분의 0을 삽입하는 쌍선형 변환을 사용하여 디지털 도메인으로 변환됩니다.

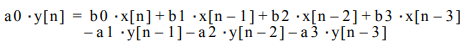

디지털 보정기 전송 기능은 다음과 같습니다.

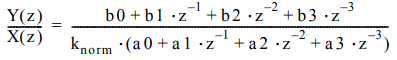

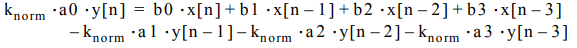

이것은 다음 미분 방정식에 해당합니다.

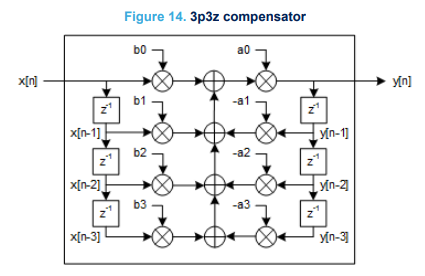

도식적으로 위의 내용은 그림 14와 같이 나타낼 수 있습니다. 이것은 디지털 IIR 필터의 직접적인 형태 1 구현으로 알려져 있습니다.

그림 14

z-1로 표시된 상자는 한 샘플 기간의 지연을 나타냅니다. 피드포워드 계수 b0, b1, b2 및 b3은 각각 현재 및 지연된 입력 샘플 x[n], x[n-1], x[n-2] 및 x[n-3]과 곱해집니다.

피드백 계수 -a1, -a2 및 -a3에는 지연된 출력 샘플 y[n-1], y[n-2] 및 y[n-3]이 각각 곱해집니다.

이러한 곱셈의 결과는 함께 합산되어 다음 출력 샘플 y[n]을 얻습니다. 계수 a0은 일반적으로 1이지만 필요한 경우 다른 값으로 설정할 수 있습니다. 다음 섹션 Normalising the coefficients를 참조하십시오.

Calculating the coefficients

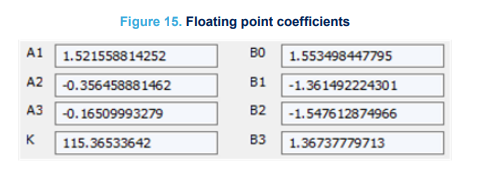

계수는 손으로 계산하거나 적절한 소프트웨어 도구를 사용하여 계산할 수 있습니다. 이 예에서 Biricha WDS는 벅 컨버터 사양과 위 섹션 벅 컨버터 사양에 나열된 아날로그 ADC 및 PWM 특성에서 시작하는 계수를 생성하는 데 사용됩니다. 부동 소수점 형식의 계수는 그림 15와 같이 WDS 도구에서 얻을 수 있습니다.

그림 15

Note : a0 계수는 암시적이며 값이 1이고 계수 A1, A2 및 A3은 도구에 의해 이미 무효화되었습니다. 즉, -a1 = A1, -a2 = A2 및 -a3 = A3입니다.

Gain compensation

다음으로 피드백 경로의 이득을 보상해야 합니다. 이 예에는 세 가지 이득 요인이 개입되어 있습니다.

1. ADC 입력 전압 분배기 비율 R2/(R1+R2): 0.19

2. 전체 디지털 출력을 전체 범위 기준 전압으로 나눈 ADC 변환 이득: 4095/3.3

3. PWM 이득은 1V 풀 스케일로 정규화되었습니다. 즉. 1V를 PWM 주기 카운트로 나눈 클록 틱: 1/27200

결합 이득은 위의 세 가지 요소의 곱입니다. 따라서 피드백 경로에서 단일 이득을 얻으려면 그림 9. 벅 컨버터와 같이 보상 이득 K를 적용해야 합니다. 여기서 K = (1/0.19) x (3.3/4095) x 27200 = 115.37입니다.

이것은 그림 15. 부동 소수점 계수에서 Biricha WDS에 의해 계산된 계수 K의 의미입니다.

게인은 FMAC의 출력에서 소프트웨어로 적용할 수 있습니다. 그러나 CPU 시간을 조금 더 절약하기 위해 다음과 같이 하드웨어에 적용할 수 있습니다. 계수 K는 KADC와 Kfilter의 두 가지로 나뉩니다. 여기서 KADC x Kfilter = K입니다.

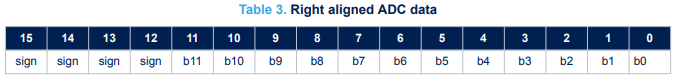

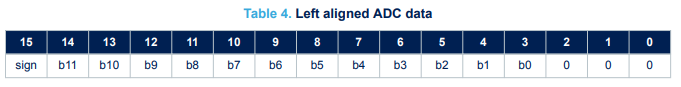

ADC에서는 왼쪽 맞춤 기능을 사용하여 계수 KADC = 8을 적용합니다. ADC 결과(오프셋을 뺀 후)는 12비트 부호 있는 정수입니다. 오른쪽 정렬 형식에서 결과는 16비트로 부호 확장됩니다.

표 3

왼쪽 정렬 모드에서 결과는 3만큼 왼쪽으로 이동하고 하나의 부호 비트만 유지합니다.

표 4

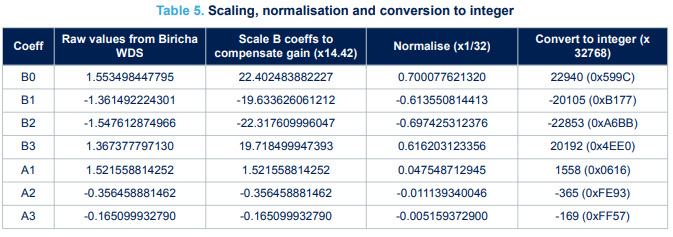

따라서 ADC 결과를 왼쪽 정렬하여 8을 곱했습니다. 나머지 이득 계수 Kfilter = K/KADC = 115.37/8 = 14.42는 분자 계수를 곱하여 필터에 적용할 수 있습니다(표 5. 스케일링, 정규화 및 정수로 변환).

필터에 전체 이득 계수 K를 적용하는 것이 가능합니다. 그러나 다음 섹션에서 설명하는 이유 때문에 분모 계수를 128로 축소해야 하므로 극 위치의 정밀도가 크게 손실되고 루프가 불안정해질 수 있습니다.

Normalising the coefficients

앞서 언급했듯이 FMAC는 고정 소수점 산술을 사용하며 계수는 '정규화'되어야 합니다. 즉, 하드웨어에서 요구하는 숫자 범위에 맞게 크기가 조정됩니다. FMAC의 경우 계수는 q1.15 형식(1 부호 비트, 15 분수 비트)으로 정의되며, 숫자 범위는 -1이며 2의 보수 정수 값 -32768(0x8000)로 표시됩니다. +1 - 2-15, 2의 보수 정수 값 32767(0x7FFF)로 표시됩니다.

몇몇 부동 소수점 계수는 1보다 크거나 -1보다 작으므로 모든 계수는 가장 큰 계수의 크기가 1보다 작도록 스케일링되어야 합니다. 이상적으로는 스케일링 계수 knorm을 사용하도록 선택해야 합니다. 고정 소수점 형식에서 사용할 수 있는 최대 정밀도입니다. 즉, 가장 큰 계수의 크기가 |B0|이면 knorm = of 1/|B0| 새로운 최대 계수 크기는 1이 됩니다. 그러나 FMAC에서 분모에 사용되는 스케일링 계수는 2의 음의 거듭제곱(1, 1/2, 1/4, ...)으로 제한됩니다. 그 이유는 a0 계수의 특정 특성과 관련이 있습니다. 3p3z 보정기에 대한 전달 함수를 다시 고려하십시오.

스케일링 계수 knorm이 분모에 적용 되면 전달 함수는 다음과 같습니다.

이것은 다음 미분 방정식에 해당합니다.

따라서 필터의 출력은 지연된 출력 샘플과 마찬가지로 knorm에 의해 조정됩니다. 스케일링을 보정하려면 계수 a0을 1/knorm으로 설정해야 합니다. 위 방정식의 좌변은 y[n]으로 줄어듭니다.

FMAC에서 계수 a0은 왼쪽 시프트를 사용하여 적용되므로 1, 2, 4,... 값만 사용할 수 있습니다. 따라서 1, 1/2, 1/4 ... 등의 knorm 값만 사용할 수 있습니다.

위에서 설명한 대로 분모 계수만 조정되면 필터 이득에 1/knorm을 곱합니다. 이를 방지하려면 분자 계수(b0, b1, b2, b3)를 분모와 동일한 계수로 스케일링해야 합니다.

이 예에서 B0 = 1.553이 가장 큰 계수입니다. 잔류 이득 보상 Kfilter를 곱하면 B0' = B0 x 14.42 = 22.40이 됩니다. B0' x 2-n < 1인 n의 가장 낮은 값은 n = 5이며 knorm = 1/32가 됩니다. 따라서 표 5. 스케일링, 정규화 및 정수로의 변환에 표시된 대로 모든 계수를 32로 나눕니다. A0은 5만큼 왼쪽 시프트에 해당하는 32로 설정됩니다.

Conversion to fixed point integer format

이제 계수가 정규화되었으므로 16비트 정수 형식으로 변환해야 합니다. q1.15에서 1의 값은 32768의 정수 값에 해당한다는 점을 염두에 두고 모든 계수에 32768을 곱하고 가장 가까운 정수로 반올림하면 됩니다.

표 5는 계수의 정수 값과 위에서 설명한 각 단계 후의 중간 값을 보여줍니다.

표 5

정수로 변환하면 필터의 전달 함수에 상당한 영향을 줄 수 있는 반올림 오류가 발생합니다. 계수는 상수로 정의됩니다.

#define B0 (0x599C)

#define B1 (0xB177)

#define B2 (0xA6BB)

#define B3 (0x4EE0)

#define A1 (0x0616)

#define A2 (0xFE93)

#define A3 (0xFF57)

또한 왼쪽 시프트 log2 A0 = 5를 정의해야 합니다.

#define KC_shift (5)

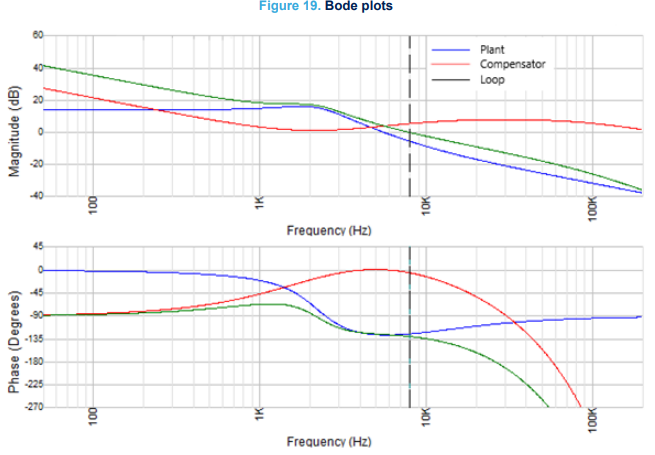

Bode plots

플랜트(벅 컨버터), 보상기 및 루프 응답(둘의 곱)의 보드 플롯은 그림 19 보드 플롯(Biricha WDS의 "주파수 응답" 탭에서 가져옴)에 나와 있습니다.

보정기는 다음 기능을 수행합니다.

1. 루프 Fx의 제로 게인 크로싱 주파수를 8kHz로 설정합니다.

2. Fx에서 위상 마진을 50dB로 설정합니다.

3. Fx에서 게인 슬로프를 -20dB/decade로 설정합니다.

이는 Bode 플롯을 검사하여 확인할 수 있습니다.

그림 19

Compensator output and PWM duty cycle

보상기 출력은 요청된 PWM 듀티 사이클입니다. DMA를 통해 고해상도 타이머로 직접 전송할 수 있습니다. 그러나 FMAC(포화 활성화)의 출력 범위는 -32768(0x8000) ~ +32767(0xFFFF)입니다.

HR 타이머 듀티 사이클은 0% ~ 90% 범위로 제한됩니다. 100% 듀티 사이클은 200kHz에서의 기간에 해당하며, 이는 27200 마스터 클록 틱(벅 컨버터 사양 섹션 참조)이므로 90%에서 최대 듀티 사이클은 24480 틱이며 상수로 정의됩니다.

#define DUTY_TICKS_MAX 24480

대부분의 주파수에 대한 보상기의 이득은 >0dB입니다. 이는 신속한 수렴을 보장하는 데 유용하지만 출력이 최대 듀티 사이클을 초과하거나 음수가 되어 PWM 신호의 예기치 않은 동작을 초래할 수 있다는 단점이 있습니다.

따라서 안전을 위해 FMAC는 FMAC 출력(RDATA 레지스터)에서 듀티 사이클을 읽고 HRTimer 비교기 1로 전송하기 전에 듀티 사이클을 > 0으로 제한하는 프로세서에 인터럽트를 생성하도록 구성됩니다.

void FMAC_IRQHandler(void) /* FMAC interrupt handler */

{

int32_t tmp;

tmp = READ_REG(hfmac.Instance->RDATA);

tmp = (tmp > 0x00007FFF ? 0 : tmp);

__HAL_HRTIM_SETCOMPARE(&hhrtim1, HRTIM_TIMERINDEX_TIMER_C, HRTIM_COMPAREUNIT_1, tmp);

}이 시점에서 CPU의 개입을 통해 소프트웨어는 오류를 감지하고 수정할 수 있습니다.

카운터가 DUTY_TICKS_MAX에 도달하면 PWM 출력을 재설정하도록 프로그래밍된 두 번째 비교기(Comparator)를 사용하여 최대 듀티 사이클 제한이 HRTimer(High Resolution timer) 자체에 적용됩니다.

<계속>

'▶ STM32 > Peripheral' 카테고리의 다른 글

| FMAC 디지털 필터 구현 방법 (with the STM32 G4 MCU Package)(7) - 3p3z (0) | 2023.12.29 |

|---|---|

| FMAC 디지털 필터 구현 방법 (with the STM32 G4 MCU Package)(6) - 3p3z code (0) | 2023.12.29 |

| FMAC 디지털 필터 구현 방법 (with the STM32 G4 MCU Package)(4) - 3p3z (0) | 2023.12.29 |

| FMAC 디지털 필터 구현 방법 (with the STM32 G4 MCU Package)(3) - FIR filter (0) | 2023.12.29 |

| FMAC 디지털 필터 구현 방법 (with the STM32 G4 MCU Package)(2) - FIR adaptive (0) | 2023.12.29 |