ADC의 Conversion 시간은 회로 설계 뿐 아니라 소프트웨어 구현시 중요한 요소입니다. 특히 빠른 응답이 필요로하는 어플리케이션에서는 이 변환시간에 대해 좀 더 주의를 해야합니다. 너무 짧게 설정하여 정확하지 않은 결과값을 가지지 않도록 해야하며, 너무 길게 설정하여 어플리케이션 수행에 장애가 되지 않도록 하여야합니다.

그림1. STM32는 SAR 방식의 ADC 가 내장되어 있습니다.

STM32는 SAR 방식의 AD Conversion Controller를 가지고 있으며 이 방식은 대표적으로 가격 대비 좋은 성능을 가진 방식입니다. 위의 그림1에서 볼 수 있듯이 여러개(합계:2C)의 Capacitor 을 가지고 있으며 이 Capacitor를 충전한 후 각 Capacitor를 설정한 비트 수 만큼 스위칭하여 비교기를 거쳐 VREF와의 비교값을 찾아내는 방식으로 되어 있습니다.

따라서, 이런 방식은 두가지의 시간이 필연적으로 필요하게 됩니다.

1. Sampling Time

내부의 Capacitor들을 충전하는 시간입니다. 이 시간은 개발자가 수동으로 정하여 ADC Control register에 설정하여야 합니다. 외부에서 들어오는 VIN의 임피던스에 따라 내부 Capacitor들이 만충되는 시간이 다르기 때문에 계산된 값이나 실험적으로 추정한 값으로 설정하여야 합니다.

예) 개발자는 보통 2.5, 6.5, 12.5, 24.5, 47.5, 92.5, 247.5, 640.5 cycle 중에서 선택할 수 있습니다.

2. Conversion Time(Hold state)

두번째는 충전된 Capacitor의 값과 VREF와 비교하는 Conversion 시간입니다. 이 시간은 개발자가 AD 변환을 위해 설정한 Resolution(분해능)에 따라 달라집니다. 만약 12bits Resolution을 설정하였다면 12.5 adc cycle이 필요하게 됩니다.

따라서 ADC Clock에 따라서 Total cycles = Sampling Time + Conversion Time 이 결정되게 됩니다.

예시)

2.5 sampling, 12bit resolution, 60 MHz ADCCLK 의 total conversion time 은

(2.5 cycle + 12.5 cycle) x 16.6 ns = 249 ns

Continuous conversion 모드일 경우 1/249 ns = 4.01 Msps 이 되게 됩니다.

3. Sampling time 결정하기

ADC 변환 시간을 줄이기 위해서는 위에 언급한 Sampling Time을 최적화하거나, 소프트웨어에서 필요한 것보다 지나치게 높은 Resolution(분해능)을 보다는 적절한 Resolution을 사용하는 방법이 있습니다.

Resolution의 경우는 어플리케이션에 따라 개발자가 결정하면 되지만 적절한 Sampling time을 찾는 것은 경험적이고 실험적인 방법(실제 스코프로 확인)과 아울러 계산을 통해서 예측할 수도 있습니다.

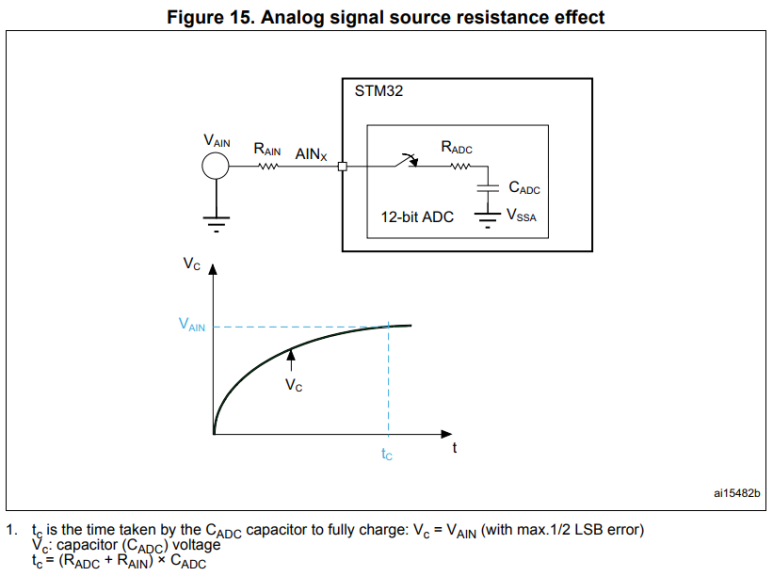

흔히 ADC는 그림2처럼 구성되는데 아날로그 신호의 임피던스 혹은 VAIN과 AINx 사이의 RAIN은 전압 강하(Drop)를 일으킵니다. 이후 RADC 앞의 Switch 가 닫히면 CADC가 충전되기 시작하며 그림2의 계산식으로 CADC의 충전 시간을 유추해 볼 수 있습니다.

그림2. ADC 충전 그래프

통상적으로 CADC는 5pF 정도이며, RADC는 Channel의 속도에 따라 몇 백 옴입니다.

4. ADC Trigger

STM32는 보통 소프트웨어, 외부 하드웨어 2가지의 트리거(Trigger) 방식을 가지고 있습니다. 소프트웨어 트리거는 코드 실행중에 ADC 레지스터에 소프트웨어 트리거를 기록하는 것으로 Conversion을 실행하는 것이고 하드웨어 트리거는 다양한 외부 트리거 소스로 부터의 이벤트로 Conversion을 실행하는 방법입니다.

외부의 하드웨어 트리거 소스는 보통 Timer update 이벤트나 Compare 이벤트를 많이 사용하게됩니다. 해당 이벤트가 발생하면 ADC는 Sampling + Conversion을 거쳐 DR(데이터 레지스터)에 변환값을 쓰게 됩니다.

5. ADC Data 가져오기

소프트웨어 트리거이든 하드웨어 트리거이든 ADC Conversion이 완료되는 시점에 DR에는 변환값이 써지게 됩니다. 이때 Data를 읽기 위해서 보통 세가지 방법을 사용하게 됩니다.

- SR(상태 레지스터)를 계속 확인하여 Conversion을 완료를 알아내어 DR에서 직접 읽어 오는 방법

- 미리 Interrupt를 설정하여 Conversion이 완료시 Interrupt를 발생시키고 해당 IRQ에서 DR을 읽는 방법

- DMA를 설정하여 Conversion 완료시 DMA를 통해 DR의 내용을 설정한 메모리에 자동으로 쓰게하는 방법

첫번째 방식은 CPU의 로드가 가장 많이 발생하는 통상적인 Polling 방식이며, 두번째 Interrupt 방식은 제때 IRQ를 처리하지 못하면 Overrun을 발생시킬 수도 있으며 interrupt 오버헤드를 증가시킵니다. 소프트웨어의 Load 및 Overrun을 없애기 위해서는 세번째 DMA 방법이 압도적으로 좋습니다.

이상 입니다.

'▶ STM32 > Peripheral' 카테고리의 다른 글

| Buck current mode with the B-G474E-DPOW1 Discovery kit (2) - Digital peak current mode (0) | 2023.12.23 |

|---|---|

| Buck current mode with the B-G474E-DPOW1 Discovery kit (1) - Principle (0) | 2023.12.23 |

| UART(USART) Printf - HAL & Polling (0) | 2023.12.13 |

| STM32 Window watchdog 멈추기 (0) | 2023.12.13 |

| STM32 에서 ADC Polling conversion 하는 방법(2) (1) | 2023.12.08 |