고성능 STM32에 포함되어 있는 MPU(Memory protection unit) 를 설명하고 있는 어플리케이션 노트 AN4838을 번역기를 돌려 올리도록 하겠습니다.

Managing memory protection unit in STM32 MCUs

Introduction

이 애플리케이션 노트는 STM32 제품에서 메모리 보호 장치(MPU)를 관리하는 방법을 설명합니다. MPU는 메모리 보호를 위한 선택적 구성 요소입니다. STM32 마이크로컨트롤러(MCU)에 MPU를 포함하면 더 강력하고 안정적입니다.

MPU를 사용하기 전에 프로그래밍하고 활성화해야 합니다. MPU가 활성화되지 않은 경우 메모리 시스템 동작에는 변경 사항이 없습니다.

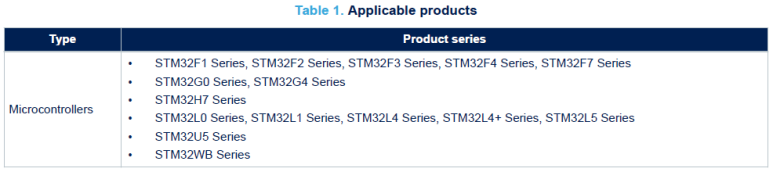

이 애플리케이션 노트는 MPU를 지원하는 Cortex®-M0+/M3/M4 및 M7 설계를 포함하는 표 1에 나열된 모든 STM32 제품에 관한 것입니다.

Overview

MPU는 다음과 같은 방법으로 임베디드 시스템을 보다 강력하고 안전하게 만드는 데 사용할 수 있습니다.

• 사용자 응용 프로그램이 중요한 작업(예: 운영 체제 커널)에서 사용하는 데이터를 손상시키는 것을 금지합니다.

• 코드 삽입 공격을 방지하기 위해 SRAM 메모리 영역을 실행 불가(XN 실행 안 함)로 정의

• 메모리 액세스 속성 변경.

MPU는 최대 16개의 메모리 영역을 보호하는 데 사용할 수 있습니다. Armv6 및 Armv7 아키텍처(Cortex-M0+, M3, M4, M7)에서 영역이 256바이트 이상인 경우 이 영역은 차례로 8개의 하위 영역을 가질 수 있습니다. 보호되는 영역의 정확한 크기는 STM32의 코어와 장치 간에 다를 수 있습니다. 자세한 내용은 표 1을 참조하십시오.

하위 영역은 항상 크기가 같으며 하위 영역 번호로 활성화 또는 비활성화할 수 있습니다. 최소 영역 크기는 캐시 라인 길이(32바이트)에 의해 결정되므로 32바이트의 8개 하위 영역은 256바이트 크기에 해당합니다.

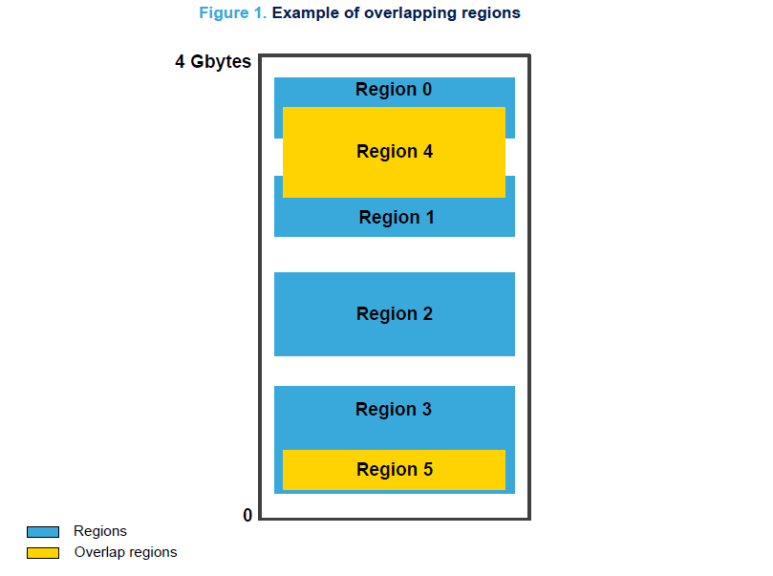

메모리 영역은 0부터 15까지 번호가 지정됩니다. 또한 기본 영역이라고 하는 id가 -1인 영역이 있습니다. 모든 0-15 메모리 영역이 기본 영역보다 우선합니다. 영역이 겹칠 수 있고 중첩될 수 있습니다. 영역 15는 가장 높은 우선 순위를 가지며 영역 0은 가장 낮은 우선 순위를 가지며 이는 영역이 겹치는 방식을 제어합니다. 우선 순위는 고정되어 있으며 변경할 수 없습니다.

Armv8 아키텍처(Cortex-M33)에서 영역은 기본 및 제한 주소를 사용하여 정의되어 개발자가 구성하는 과정에서 유연성과 단순성을 제공합니다. 또한 Cortex-M33에는 영역 크기가 더 유연해지기 때문에 하위 영역이 포함되지 않습니다. 아래 그림은 6개 영역이 있는 예를 보여줍니다. 이 예는 영역 4가 영역 0과 영역 1과 겹치는 것을 보여줍니다. 영역 5는 영역 3 안에 완전히 둘러싸여 있습니다. 우선 순위가 오름차순이므로 겹치는 영역(주황색)이 우선 순위를 갖습니다. 따라서 영역 0은 쓰기 가능하고 영역 4는 쓰기 가능하지 않은 경우 0과 4 사이의 오버랩에 해당하는 주소는 쓰기 불가능합니다.

주의: Armv8 아키텍처(Cortex-M33)에서는 영역이 겹칠 수 없습니다. MPU 영역 정의가 훨씬 더 유연하므로 MPU 영역을 중복할 필요가 없어졌습니다.

MPU가 통합되어 데이터와 명령어를 위한 별도의 영역이 없습니다. MPU는 시스템 수준 캐시 장치 또는 메모리 컨트롤러로 내보낼 수 있는 캐시 가능성과 같은 다른 메모리 속성을 정의하는 데에도 사용할 수 있습니다.

Arm 아키텍처의 메모리 속성 설정은 내부 캐시와 외부 캐시의 두 가지 수준의 캐시를 지원할 수 있습니다. STM32F7 및 STM32H7 시리즈의 경우 한 수준의 캐시(L1-캐시)만 지원됩니다.

캐시 제어는 캐시 제어 레지스터에 의해 전역적으로 수행되지만 MPU는 캐시 정책과 영역이 캐시 가능한지 여부를 지정할 수 있습니다.

Memory model

STM32 제품에서 프로세서에는 최대 4GB의 주소 지정 가능 메모리를 제공하는 고정 기본 메모리 맵이 있습니다.

메모리 맵과 MPU의 프로그래밍은 메모리 맵을 영역으로 분할합니다. 각 영역에는 정의된 메모리 유형(Type)과 메모리 속성(Attribute)이 있습니다. 메모리 유형 및 속성은 영역에 대한 액세스 동작을 결정합니다.

Memory types

세 가지 일반적인 메모리 유형이 있습니다.

• Normal 메모리: 바이트, Half words 및 Words의 로드 및 저장이 CPU에 의해 효율적인 방식으로 정렬되도록 허용합니다(컴파일러는 메모리 영역 유형을 인식하지 못함). 일반 메모리 영역의 경우 로드/저장이 프로그램에 나열된 순서대로 CPU에서 반드시 수행되는 것은 아닙니다.

• Device 메모리: 장치 영역 내에서 로드 및 저장이 엄격하게 순서대로 수행됩니다. 이는 레지스터가 올바른 순서로 설정되었는지 확인하기 위한 것입니다.

• Strong ordered 메모리: 모든 것이 항상 프로그래밍 방식으로 나열된 순서대로 수행됩니다. 여기서 CPU는 프로그램 스트림에서 다음 명령을 실행하기 전에 로드/저장 명령 실행(유효 버스 액세스)이 끝날 때까지 기다립니다. 이로 인해 성능이 저하될 수 있습니다.

Memory attributes

영역 속성 및 크기 레지스터(MPU_RASR)는 모든 메모리 속성이 설정되는 곳입니다. 표는 MPU_RASR 레지스터의 영역 속성과 크기에 대한 간략한 설명을 보여줍니다.

이전 표의 매개변수는 아래에 자세히 설명되어 있습니다.

• XN 플래그는 코드 실행을 제어합니다. 영역 내에서 명령을 실행하려면 권한 수준에 대한 읽기 액세스가 있어야 하고 XN은 0이어야 합니다. 그렇지 않으면 MemManage 오류가 생성됩니다.

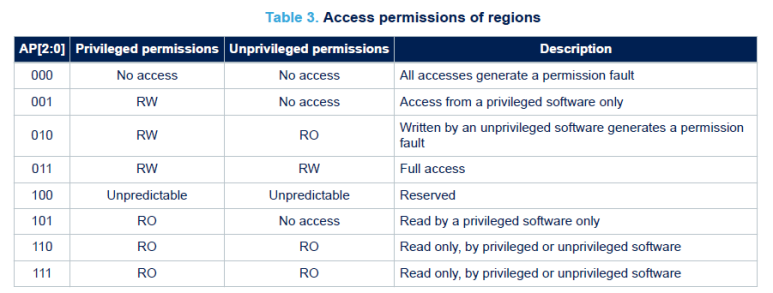

• 데이터 접근 권한(AP) 필드는 메모리 영역의 AP를 정의합니다. 아래 표는 액세스 권한을 보여줍니다.

• S 필드는 공유 가능한 메모리 영역을 위한 것입니다. 메모리 시스템은 다중 버스 마스터가 있는 시스템(예: DMA 컨트롤러가 있는 프로세서)에서 버스 마스터 간에 데이터 동기화를 제공합니다.

Strong ordered 메모리는 항상 공유할 수 있습니다. 여러 버스 마스터가 공유할 수 없는 메모리 영역에 액세스할 수 있는 경우 소프트웨어는 버스 마스터 간의 데이터 일관성을 보장해야 합니다. STM32F7 시리즈 및 STM32H7 시리즈는 하드웨어 일관성을 지원하지 않습니다. S 필드는 캐시할 수 없는 메모리와 동일합니다.

• TEX, C 및 B 비트는 영역에 대한 캐시 속성과 어느 정도 공유 가능성을 정의하는 데 사용됩니다. 다음 표에 따라 인코딩됩니다.

• 하위 영역 비활성화 비트(SRD) 플래그는 특정 하위 영역의 활성화 여부를 나타냅니다. 하위 영역을 비활성화하면 비활성화된 범위와 겹치는 다른 영역이 대신 일치합니다. 다른 활성화된 영역이 비활성화된 하위 영역과 겹치지 않으면 MPU에서 오류가 발생합니다.

캐시를 구현하는 제품의 경우(L1 캐시를 구현하는 STM32F7 시리즈 및 STM32H7 시리즈에만 해당) 추가 메모리 속성은 다음과 같습니다.

• Cacheable/non-cacheable: 전용 영역을 캐시할 수 있는지 여부를 의미합니다.

• Write through with no write allocate(쓰기 할당 없이 연속 쓰기): 적중 시 캐시와 주 메모리에 씁니다. 놓쳤을 때 해당 블록을 캐시로 가져오지 않는 주 메모리의 블록을 업데이트합니다.

• Write-back with no wrtied allocat(쓰기 할당이 없는 다시 쓰기): 적중 시 블록에 대한 캐시 설정 더티 비트에 기록하고 주 메모리는 업데이트되지 않습니다. 실패 시 주 메모리의 블록을 업데이트하여 해당 블록을 캐시로 가져오지 않습니다.

• Write-back with write and read allocate(쓰기 및 읽기 할당을 통한 후 기입): 적중 시 블록에 대한 캐시 설정 더티 비트에 씁니다. 주 메모리는 업데이트되지 않습니다. 놓쳤을 때 메인 메모리의 블록을 업데이트하고 블록을 캐시로 가져옵니다.

참고: Cortex-M7의 경우 TCM 메모리는 TCM에 보관된 주소를 포함하는 메모리 영역에 대해 MPU에 정의된 메모리 유형 속성에 관계없이 항상 캐시 불가능, 비공유 일반 메모리로 작동합니다.

그렇지 않으면 TCM 주소 공간의 MPU 영역과 연결된 액세스 권한은 TCM 주소 공간 외부의 주소와 동일한 방식으로 처리됩니다.

Cortex-M7 constraint speculative prefetch

Cortex-M7은 일반 메모리 위치(예: FMC, Quad-SPI 장치)에 대한 추측 액세스를 허용하는 추측 프리페치 기능을 구현합니다.

위험한 프리페치가 발생하면 다중 액세스에 민감한 메모리나 장치(예: FIFO, LCD 컨트롤러)에 영향을 줄 수 있습니다. 또한 예측/추측성 프리페치가 발생할 때 더 높은 대역폭을 사용하는 LCD-TFT 또는 DMA2D와 같은 다른 마스터에서 생성된 트래픽을 방해할 수도 있습니다.

추측성 프리페치로부터 일반 메모리를 보호하기 위해 메모리 속성을 일반에서 Strong ordered로 변경하거나 MPU의 메모리 타입을 Device 메모리로 변경하는 것이 좋습니다. 메모리 속성 구성에 대한 자세한 내용은 Armv6 및 Armv7 아키텍처에서 STM32Cube HAL을 사용한 섹션 6 MPU 설정 예제를 참조하십시오.

'▶ ARM Core' 카테고리의 다른 글

| IRQ Handler table을 RAM에 올리기 (0) | 2023.11.17 |

|---|---|

| [AN5557] STM32H7 dual-core architecture - Peripherals allocation (0) | 2023.11.17 |

| [AN4838] STM32 MPU (3) (0) | 2023.11.17 |

| [AN4838] STM32 MPU (2) (0) | 2023.11.17 |

| Cortex-M7 Memory Model(feat. MPU) (0) | 2023.11.17 |