Cortex-M7 아키텍쳐는 MPU를 통해 각 메모리의 유형(Type)과 속성(Attributes)를 지정할 수 있습니다. 여기서 메모리는 Internal or External 메모리를 말합니다. 메모리 맵과 MPU는 메모리 맵을 영역으로 분할합니다. 각 영역에는 정의 된 메모리 유형(type)을 가지고 있으며 일부 영역은 추가 메모리 속성(attributes)이 가지고 있습니다. 메모리 유형 및 속성은 영역에 대한 액세스 동작을 결정합니다.

다음은 STM32F7, H7 Programming manual을 번역하여 올립니다.

1. Type

- Normal : 프로세서는 효율성을 위해 트랜잭션을 재정렬하거나 추측 읽기를 수행 할 수 있습니다. 즉, 순차적으로 정렬된 Instruction 대로 실행이 되지 않을 수도 있다는 뜻입니다.

- Device and Strongly-ordered : 프로세서는 장치 또는 강력하게 정렬 된 메모리에 대한 다른 트랜잭션과 관련된 트랜잭션 순서를 유지합니다. 즉, 어떠한 개입없이 순차적으로 instruction이 수행된다는 것을 뜻합니다.

* Device와 Strongly-ordering 순서 요구 사항의 다른 점은 메모리 시스템이 Device 메모리에 대한 쓰기를 버퍼링 할 수 있지만 Strongly-ordered 메모리에 대한 쓰기를 버퍼링해서는 안됨을 의미합니다.

2. Attributes

Sharable : Sharable 메모리 영역의 경우 메모리 시스템은 여러 버스 마스터가있는 시스템 (예 : DMA 컨트롤러가있는 프로세서)에서 버스 마스터간에 데이터 동기화를 제공합니다.

Strongly-ordered 메모리는 항상 공유 할 수 있습니다.

여러 버스 마스터가 공유 할 수없는 메모리 영역에 액세스 할 수있는 경우, 소프트웨어로 버스 마스터 간의 데이터 일관성을 보장해야합니다.

Execue Never (XN) : 프로세서가 명령 액세스를 방지 함을 의미합니다. XN 메모리 영역에서 가져온 명령어를 실행할 때 HardFault 예외가 생성됩니다.

명시적 메모리 액세스 명령에 의해 발생하는 대부분의 메모리 액세스에 대해서도, 메모리 액세스 순서와 명령의 프로그램 순서가 항상 일치하지 않습니다.

어떠한 Re-ordering의 제공도 명령어 순서 동작에는 영향을 주지 못합니다. 일반적으로 의도한 프로그램 실행이 완료된 두 개의 메모리 액세스 순서에 따라 달라지는 경우, 소프트웨어는 메모리 액세스 명령 사이에 메모리 배리어 명령을 삽입해야합니다.

배리어스 명령에 대한 내요은 아래 블로그를 참조하세요.

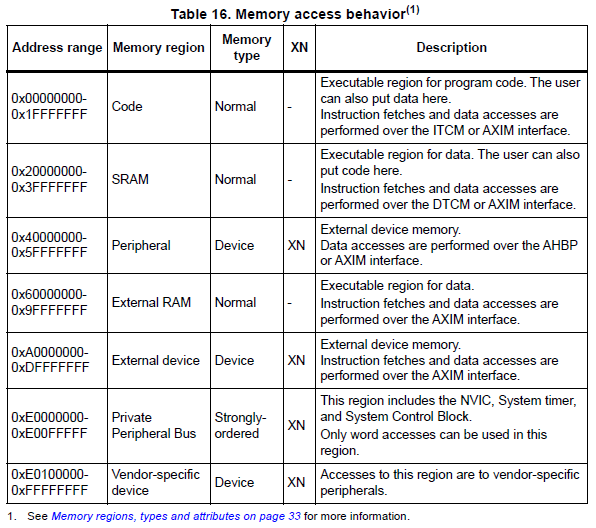

다음은 메모리 맵의 각 영역 엑세스 동작압니다.

코드, SRAM 및 외부 RAM 영역에는 프로그램이 포함될 수 있습니다.

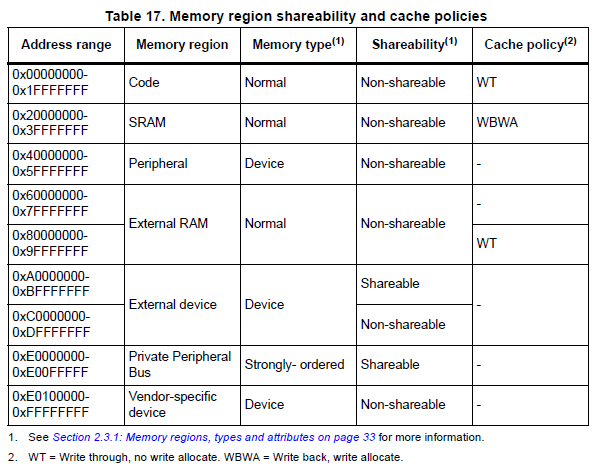

캐시 및 공유 메모리에 대한 추가 메모리 액세스 제약

시스템에 캐시 또는 공유 메모리가 포함 된 경우 일부 메모리 영역에는 추가 액세스 제한이 있으며 일부 영역은 아래표 표시된대로 세분됩니다.

'▶ ARM Core' 카테고리의 다른 글

| IRQ Handler table을 RAM에 올리기 (0) | 2023.11.17 |

|---|---|

| [AN5557] STM32H7 dual-core architecture - Peripherals allocation (0) | 2023.11.17 |

| [AN4838] STM32 MPU (3) (0) | 2023.11.17 |

| [AN4838] STM32 MPU (2) (0) | 2023.11.17 |

| [AN4838] STM32 MPU (1) (0) | 2023.11.17 |